16+ verilog vector

Copy path Copy permalink. Verilog provides the concept of Vectors.

Verilog Scalar And Vector Javatpoint

In Verilog the signals that are being concatenated do not need to be of the same type.

. Verilog-Practice 1_Verilog language 16_Vector3v Go to file Go to file T. Verilog arrays can be used to group elements into multidimensional objects to be manipulated more easily. This commit does not belong to any.

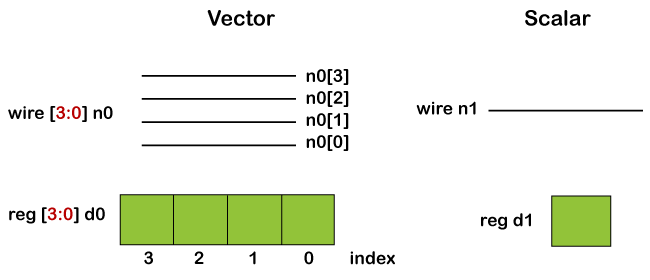

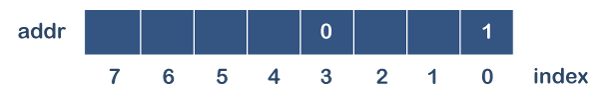

The outputs are represented by the 16-bit vector Y y0 y1y15. Vectors are used to represent multi-bit busses. In Verilog we can have an any dimension of array and can be of 2 types ie scalar and vector.

Go to line L. But in hardware many ports can have more than one bit has an input. Should be four skip bits and the eight keep bits just to the left of these should move down.

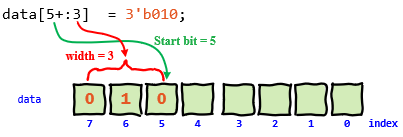

From this we can get the 4-bit ripple. A vector to represent a multi bit bus is declared as follows. Copy path Copy permalink.

Since Verilog does not have user-defined types we are restricted to. This commit does not belong to any branch on this repository and may belong. General syntax to declare a vector type.

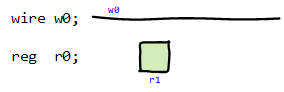

Verilog Vectors 03 Aug 2021 3 mins In Verilog we have seen that we have 1-bit data types. Go to line L. 04 Aug 2021.

VHDL is more strongly typed so concatenation in VHDL requires that types are matched. B Write Verilog HDL behavioral style code for 4-to-16 decoder by. While writing the Verilog code for 16-bit Ripple carry adder the same procedure is used.

8-bit reg vector with. The code snippet below shows the general syntax which we use to declare a vector type in verilog. A Write Verilog HDL behavioral style code for 2-to-4 decoder.

First the Verilog code for 1-bit full adder is written. MIPS is an RISC processor which is widely used by many universities in academic courses related to. Solutions-to-HDLbits-Verilog-sets 2verilog language 16vector_concatenation_operatorv Go to file Go to file T.

Array means an ordered list of variables. Now the count has five skip bits 1213141516 between the two keep sections. In this project a 16-bit single-cycle MIPS processor is implemented in Verilog HDL.

Vectors are multiple bit widths net or reg data type variables that can be declared by specifying their range.

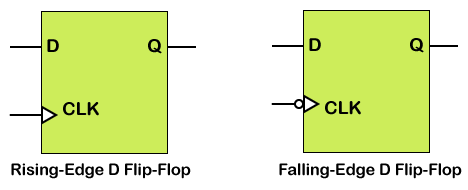

Verilog D Flip Flop Javatpoint

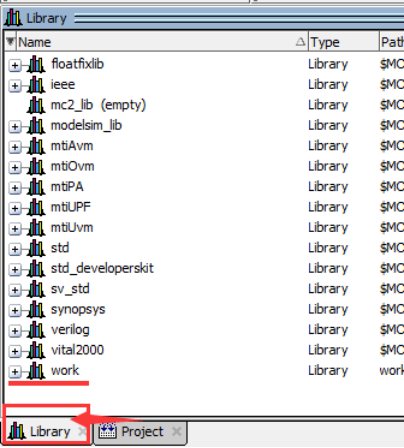

Hdl Verilog Vlsi Tutorial

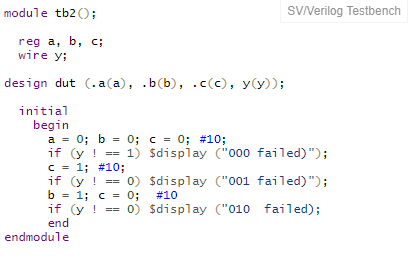

Ultimate Guide Verilog Test Bench Hardwarebee

Air Supply Lab Lesson 04 Verilog Scalar Vector And Array

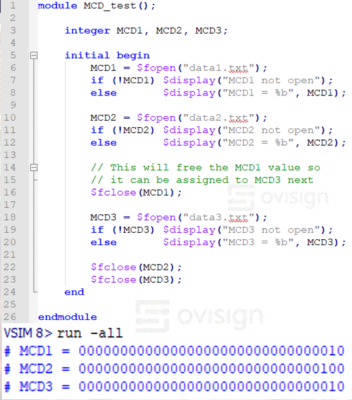

Master Verilog Write Read File Operations Part1 Ovisign

Air Supply Lab Lesson 04 Verilog Scalar Vector And Array

Verilog Scalar And Vector Javatpoint

2 To 4 Decoder In Verilog Hdl Geeksforgeeks

Fixed Point Matrix Multiplication In Verilog Full Code Tutorials Fpga4student Com

Using Xilinx Vivado Design Suite To Prepare Verilog Modules For Integration Into Labview Fpga Ni

Verilog Hdl

Verilog Testbench Not Reading Test Vector Correctly Stack Overflow

Verilog An Overview Sciencedirect Topics

How To Randomize A Queue In Systemverilog Quora

System Verilog Eenet Sv Eenet Application Modeling Block Currents In Mixed Signal Verification Blog

Multiplexers Different Ways To Implement Verilog By Examples Electrosofts Com

Vector Accelerating Unit Cu Sv At Master Alibaba Vector Accelerating Unit Github